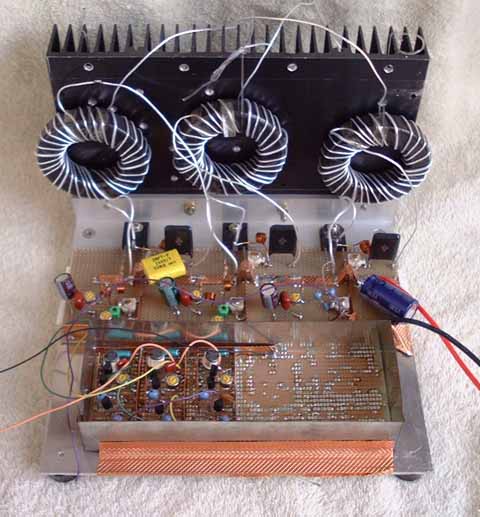

10/3/1999に5.5MHz三相交流で1000Vp-p得られた。しかし1/n発振などで不安定である。 PowerMOS1個に1Aは流さないとこの出力は得られない。60V1A=60W というわけで 無理をしているから素子がたびたび破壊した。ドレイン−ソース間ショートとなる。

10/24/1999に20.2MHzに発振を設定したが、円盤に接続すると電圧が出ない。 それでフェライトコアによる昇圧をやめて直接接続してみた。 50Vp-pは観測できているが、各相のパワーが同一になっていないと正確な三相にはならない。 原因の1つに発振器内部の各chのカブリがある。 また、各PowerMOSにも電源干渉が発生している。アースも不安定で正確な実験にならない。 20MHzの三相交流高周波送信機というわけだからそう簡単にはいかない。 作り直しとしてPowerMOSによる実験3に移行する。10/31/1999